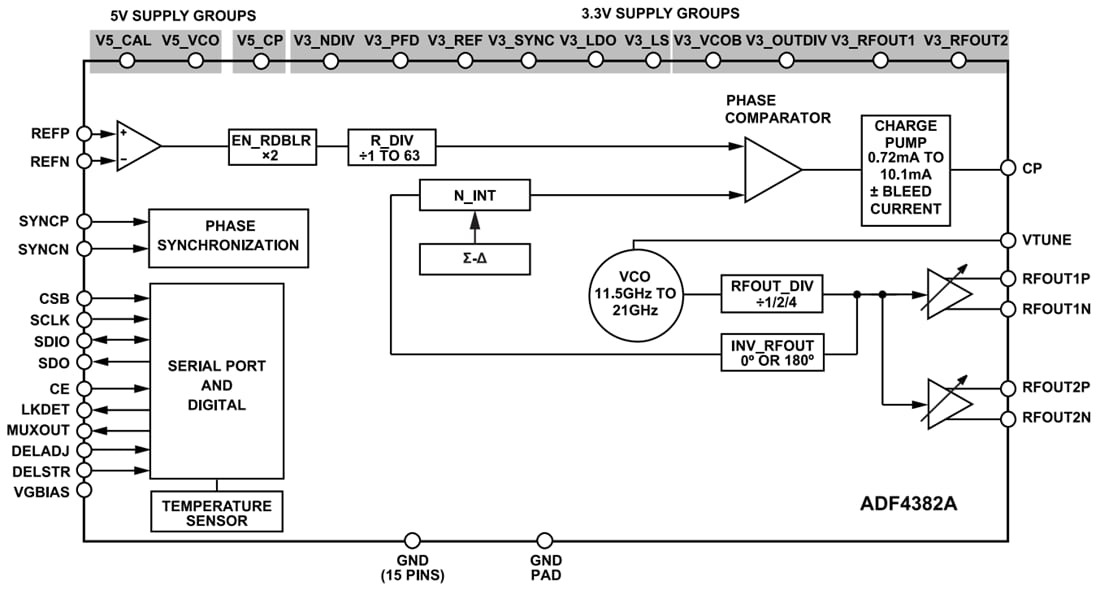

El bucle bloqueado en fase (PLL) Fractional-N ADF4382A de Analog Devices es un bucle bloqueado en fase (PLL) de fluctuación ultrabaja y alto rendimiento. Tiene un oscilador controlado por voltaje (VCO) integrado, ideal para la generación de oscilador local (LO) para aplicaciones de reloj convertidor de datos o 5G. El PLL de alto rendimiento tiene una cifra de mérito de −239 dBc/Hz, bajo ruido 1/f y un PFD de alta frecuencia de 625 MHz en modo entero que puede lograr un ruido dentro de banda ultrabaja y una fluctuación integrada. El ADF4382A puede generar frecuencias en un rango de octava fundamental de 11,5 GHz a 21 GHz, eliminando la necesidad de filtros subarmónicos. Los divisores de salida divididos en dos y cuatro del ADF4382A permiten generar frecuencias de 5,75 GHz a 10,5 GHz y de 2,875 GHz a 5,25 GHz, respectivamente.